Semiconductors

Critical Minerals and Semiconductors

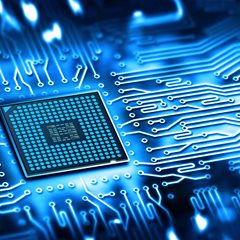

Semiconductors sit at the core of every modern electronic device, from smartphones and electric vehicles to cloud-scale AI accelerators. Their performance, efficiency, and longevity hinge on a small set of critical minerals whose unique physical and chemical properties enable precision transistor architecture, ultrafast signal transmission, and robust thermal management. Ultra-pure silicon wafers become the canvas for integrated circuits, doped with boron, phosphorus, and arsenic to sculpt nanoscale p–n junctions. Gallium, indium, and germanium expand the reach of high-speed, high-frequency, and optoelectronic components, while tantalum, tungsten, and cobalt reinforce interconnects that must move billions of electrons per second without degradation. Rare-earth elements such as neodymium and dysprosium enhance stepper lasers and high-strength magnets used in lithography and wafer handling, and copper, silver, and gold deliver low-resistance pathways for power and data. As chip geometries shrink toward the angstrom era and demand soars for AI-ready, energy-efficient processors, ensuring secure, sustainable supplies of these minerals becomes a strategic imperative. Disruptions, whether geopolitical, environmental, or technical, can ripple through entire technology value chains, stalling innovation and raising costs. Robust sourcing strategies, circular-economy recycling, and materials R&D are therefore essential to safeguarding the semiconductor ecosystem and, by extension, the digital technologies that drive global growth.

Critical Minerals used in semiconductors

Overview of Semiconductor Manufacturing

The semiconductor value chain can be understood not only as a linear process, but also through its functional categories, which define the material inputs, equipment technologies, and fabrication techniques that shape chip performance, yield, and supply chain exposure. The full manufacturing journey spans 32 discrete steps, from silicon crystal growth to final outbound logistics. These are grouped into seven functional domains, each with distinct strategic, technological, and material implications.

Below is an overview of these seven domains, including their associated process steps and strategic relevance:

1) Wafer formation & doping

Associated steps: 1, 2, 3, 4, 5, 6, 10

This phase lays the foundation for the entire semiconductor manufacturing process. It begins with the formation of high-purity silicon wafers and ends with the precise electrical tuning of their properties through doping. The accuracy achieved here directly impacts transistor performance, leakage control, and long-term device reliability. These steps create the substrate upon which every subsequent layer of the integrated circuit is built.

-

Step 1 – Silicon crystal growth: Ultra-pure polysilicon is melted in a quartz crucible and slowly cooled to grow a single-crystal silicon ingot. This is done using the Czochralski method, which yields defect-free crystals with tightly controlled electrical resistivity.

-

Step 2 – Ingot trim and grind: The ends of the ingot, known as the seed and tail, are trimmed to remove defects introduced at the beginning and end of crystal pulling. The ingot is then centre ground to achieve a uniform diameter. Orientation flats or notches are laser-scribed to mark the crystal axis for precise alignment in later steps.

-

Step 3 – Wafer slicing and edge shaping: The cylindrical ingot is sliced into thin discs using wire saws coated with synthetic diamond abrasives. These wafers are then edge-shaped to reduce stress concentrations and minimise the risk of breakage during handling.

-

Step 4 – Wafer flattening and polishing: The sliced wafers undergo chemical mechanical planarisation (CMP) to remove surface defects and achieve the flatness required for nanometre-scale patterning.

-

Step 5 – Epitaxial layer growth: A thin, defect-free, ultra-pure silicon layer is grown atop the wafer to improve electrical performance, particularly in advanced nodes.

-

Step 6 – Pad oxidation: A thin layer of silicon dioxide is thermally grown on the wafer surface. This oxide acts as an initial insulating barrier and protects the wafer during early lithography steps. This epitaxial layer enhances device performance, especially in advanced logic and power nodes, by providing a cleaner, more controlled starting surface.

-

Step 10 – Ion implantation and anneal: Specific dopant atoms, such as boron or phosphorus, are implanted into the wafer to tailor its electrical properties. A rapid thermal annealing process then activates these dopants and heals any crystal damage caused by implantation.

Together, these steps define the resistivity, carrier concentration, and mechanical integrity of the wafer. They set the baseline for electrical performance, thermal stability, and manufacturing yield across all downstream fabrication. Even minor deviations in dopant dose or crystal quality at this stage can compromise transistor function and chip reliability.

Key terms:

-

Polysilicon: Ultra-pure silicon made up of many small crystals, used as the feedstock for single-crystal growth.

-

Czochralski process: A technique for growing large single crystals of silicon by slowly pulling a seed crystal from molten silicon.

-

Doping: The addition of specific atoms to silicon to modify its electrical conductivity.

-

Epitaxy: The growth of a thin crystal layer that precisely matches the structure of the substrate underneath.

-

Annealing: A high-temperature treatment used to repair crystal damage and activate implanted dopants.

2) Active device layers

Associated steps: 8, 12, 13, 14

This section focuses on building the transistor structures that act as the active switching elements in integrated circuits. A transistor is a nanoscale electrical switch that controls the flow of current, enabling operations like logic processing, memory storage, and signal amplification. These fabrication steps define each transistor’s geometry, electrical characteristics, and conductive pathways. These steps are critical in determining the speed, power efficiency, and scalability of the transistor.

-

Step 8 – Fin or nanosheet fabrication and channel release: In advanced CMOS (complementary metal-oxide-semiconductor) nodes, transistors are formed using three-dimensional architectures. In FinFETs (Fin Field-Effect Transistors), channels are built as vertical fins of silicon to increase surface area and gate control. In newer gate-all-around (GAA) nanosheet devices, horizontal sheets are stacked and suspended above the wafer by selectively removing underlying sacrificial layers. These structures improve gate-channel contact and reduce current leakage. The process includes high-precision lithography, anisotropic etching of silicon, and channel release for nanosheet designs.

-

Step 12 – Spacer deposition and etch-back: A conformal dielectric film, often made of silicon nitride or silicon oxynitride, is deposited around the gate area. It is then anisotropically etched to form sidewall spacers. These thin insulating barriers define the lateral distance between the gate and the source/drain and play a crucial role in leakage control, electrical isolation, and implantation masking during later steps.

-

Step 13 – Source/drain epitaxy and junction engineering: Heavily doped semiconductor regions, known as source and drain, are grown selectively next to the transistor channel using epitaxial deposition. Materials like silicon-germanium (SiGe) or silicon-phosphorus (Si:P) are commonly used to introduce strain engineering, which enhances carrier mobility. The doping concentration and profile are carefully controlled to balance drive current, switching speed, and electrostatic integrity.

-

Step 14 – Silicidation: A thin metal layer, typically nickel (Ni), cobalt (Co), or platinum (Pt), is deposited onto exposed silicon in the source, drain, and gate areas. The metal reacts with the silicon to form a metal silicide, a low-resistance compound that significantly improves electrical contact between the silicon junctions and the overlying metal interconnects. This step is critical to reducing contact resistance and power loss.

As chipmakers move to ever-smaller nodes, this phase becomes increasingly important for delivering high-performance logic and low-power designs that meet modern application demands. These fabrication steps define the electrical switching behaviour of every transistor on the chip. The dimensions and material interfaces created here operate at scales below 10 nanometres, requiring sub-nanometre alignment accuracy. These challenges make this phase one of the most geometrically demanding in the semiconductor process and directly impact final device performance, leakage, and scaling potential at advanced technology nodes.

Key terms:

-

Transistor: A tiny switch that controls the flow of electrical current in a chip.

-

FinFET/nanosheet: 3D transistor designs that increase control over current and reduce leakage, enabling faster, more efficient devices.

-

Spacers: Thin insulating walls placed alongside the gate to precisely define the transistor’s structure.

-

Epitaxy: A technique for growing doped crystalline silicon in specific regions to form source and drain.

-

Silicide: A low-resistance compound formed by reacting metal with silicon to create better electrical contact.

3) Gate stack (high-k & ferroelectric)

Associated step: 11

The gate stack is one of the most important components in a modern transistor. It functions as the on/off switch, controlling how and when electrical current flows through the channel. In advanced semiconductor nodes, this structure is engineered using specialised materials that enable better performance, lower leakage, and higher energy efficiency.

Step 11 – Gate stack formation (high-k / metal gate):

Historically, transistors used silicon dioxide (SiO₂) as the gate insulator and doped polysilicon as the gate electrode. However, as transistors became smaller, SiO₂ became too thin to prevent unwanted current leakage. To overcome this, modern gate stacks now use high-k dielectric materials, such as hafnium oxide (HfO₂) or zirconium oxide (ZrO₂), which offer superior insulation even at greater thicknesses. These high-k materials reduce leakage and allow continued transistor scaling.

Alongside the high-k layer, the gate’s conductive component is also upgraded. Instead of polysilicon, the gate electrode is now formed from metals like titanium nitride (TiN), tungsten (W), or ruthenium (Ru). These metals provide lower resistance, better compatibility with the high-k dielectric, and improved performance, particularly at smaller dimensions.

In the most advanced applications, the gate stack can also include ferroelectric materials, special oxides that retain their electric state even when power is removed. Ferroelectric-doped hafnium oxide, with elements such as lanthanum (La) or yttrium (Y), enables the creation of FeFETs (ferroelectric field-effect transistors). These devices combine the logic speed of traditional transistors with the data-retention capabilities of memory, making them attractive for embedded non-volatile memory and ultra-low-power logic.

The gate stack layer plays a decisive role in determining each transistor’s threshold voltage, leakage current, and switching efficiency, which are, key factors that define how fast and how power-efficient a chip will be. As scaling continues into the sub-5 nm range, gate stack engineering becomes more complex and even more essential to achieving node-to-node improvements in chip performance.

Key terms:

-

Gate stack: A layered structure in a transistor that controls the flow of current, essentially the transistor’s on/off switch.

-

High-k dielectric: An insulating material with high permittivity (ability to store electric charge), which blocks leakage current more effectively than silicon dioxide.

-

Metal gate: A conductive metal layer that replaces older polysilicon gates to improve switching speed and reduce electrical resistance.

-

Ferroelectric: A material that can hold an electric charge even when the power is turned off, enabling memory-like behaviour inside a transistor.

4) Interconnect & contacts (BEOL – Back-End-of-Line)

Associated steps: 15, 17, 20, 21

The BEOL defines the electrical pathways that allow millions to billions of transistors to function as a coherent integrated circuit. It includes both vertical interconnects (vias, contacts) and horizontal signal routing (metal layers). As chips scale down, the BEOL becomes more complex, requiring additional metal layers, finer features, and tighter spacing. Materials used here must offer excellent conductivity, electromigration resistance, and low signal delay, while remaining compatible with complex patterning, CMP, and barrier integration schemes.

This category encompasses the formation of both vertical and horizontal connections between transistors, as well as the redistribution of signals to external package interfaces. Once transistors are complete, they must be wired together into functional circuits. This is achieved during the BEOL, where a multilayer stack of metal interconnects, vias, and contacts is constructed above the silicon substrate. These connections define how signals travel between logic gates, memory blocks, and I/O pads, and are critical to the chip’s overall speed, power efficiency, and signal integrity.

-

Step 15 – Self-aligned contacts: Metal plugs are etched and filled to form vertical electrical pathways between the transistor terminals (source, drain, gate) and the first layer of wiring. These contacts are “self-aligned” to prevent shorts and maintain precise alignment with transistor features. They are typically made using tungsten (W) or cobalt (Co) and are lined with barrier materials such as titanium nitride (TiN) to prevent metal diffusion into surrounding dielectrics. Self-aligned contact structures are essential for minimising parasitic resistance and maintaining dimensional accuracy at advanced nodes.

-

Step 17 – Dual-damascene interconnects: This process builds the intricate, multi-level wiring that links all parts of the chip. This step forms the horizontal metal wiring layers that connect transistors across the chip, as well as the vertical vias that link successive layers. Using a technique called dual-damascene, both vias (vertical holes) and trenches (horizontal grooves) are etched into a low-κ dielectric material. These structures are then filled with copper (Cu), often lined with tantalum (Ta) or tantalum nitride (TaN), to form dense, low-resistance interconnects. The surface is polished flat using chemical mechanical planarisation (CMP). Multiple interconnect layers are stacked to form a high-performance signal routing network that handles data, clock, and power delivery.

-

Step 20 – Redistribution layers (RDL): RDLs are wide metal lines that reroute the fine internal connections to external bond pads. As a top-level metal routing layer built above the BEOL stack, the RDL repositions the chip’s internal wiring to match the wider pin pitch required by flip-chip, fan-out wafer-level packaging (FOWLP), or 2.5D interposer connections. These lines are typically made of copper, often plated with nickel and gold, and serve as the interface between the internal circuit and the chip package. Copper-based RDLs are used for these external-facing traces due to their high conductivity, corrosion resistance, and compatibility with solder bonding. RDLs are essential for chip-to-package alignment and are a critical enabler of high-density packaging and heterogeneous integration.

-

Step 21 – Backside metallisation: In power devices, image sensors, and high-performance logic, a metal layer—often titanium, tungsten, or copper—is deposited onto the back of the wafer. This layer provides electrical grounding, improves heat dissipation, and in some cases enables through-silicon vias (TSVs) for 3D stacking. Backside metallisation is increasingly important for thermal and power management, particularly in advanced nodes where layout density and heat flux are tightly constrained.

These steps govern resistance-capacitance (RC) delay, electromigration lifetime, and signal integrity, all of which are critical in high-density logic and memory designs. Material choices such as copper, cobalt, tantalum, and low-κ dielectrics, directly influence power delivery and circuit speed, making this one of the most performance-sensitive stages in chip manufacturing.

Key terms:

-

BEOL (Back-End-of-Line): This category encompasses the formation of vertical and horizontal connections between transistors, as well as redistribution of signals to the package interface.

-

Interconnects: Metal wires within the chip that carry signals between transistors and other circuit elements.

-

Vias: Vertical holes that connect different layers of metal wiring.

-

Dual-damascene: A fabrication technique that simultaneously creates both vias and horizontal trenches before metal filling.

-

Redistribution layer (RDL): A top-level metal layer that routes internal signals to external bonding sites.

-

Backside metallisation: Applying a metal layer to the wafer’s back to assist with grounding, thermal control, and vertical integration.

5) CMP, etch & cleaning

Associated steps: 7, 9, 16, 18, 19, 22, 23

This category includes key support processes that enable and maintain the precision required in advanced chip manufacturing. These steps are essential for shaping structures, removing unwanted materials, and keeping surfaces clean and flat throughout the front-end and back-end processes.

-

Step 7 – Shallow trench isolation (STI): To prevent electrical current from leaking between neighbouring transistors, narrow trenches are etched into the wafer and filled with an insulating oxide material. These filled trenches electrically isolate each transistor, preserving signal integrity and preventing short circuits. The surface is then polished to ensure a flat topography for the next patterning layers.

-

Step 9 – Photolithography: This is the process of transferring circuit patterns onto the wafer using light. The wafer is coated with a light-sensitive material called photoresist, then exposed to ultraviolet light through a patterned mask. After exposure, the photoresist is developed, and the underlying material is selectively etched to create the desired structures. This step is repeated dozens of times with different masks to define each circuit layer.

- Step 16 – Dielectric deposition (interlayer dielectric): Once the transistors are built, insulating materials called dielectrics are deposited between layers of metal interconnects to electrically isolate them. These insulators prevent short circuits and control parasitic capacitance. Low-κ dielectrics (materials with a low dielectric constant) are commonly used to reduce signal delay and improve energy efficiency in high-performance designs.

-

Step 18 – Chemical mechanical planarisation (CMP): As new layers are added during fabrication, the wafer surface becomes increasingly uneven. Chemical mechanical planarisation (CMP) uses a combination of chemical slurry and abrasive polishing to flatten each layer with nanometre-level precision. This planarisation is essential to maintain accurate focus in photolithography, ensure reliable metal patterning, and enable precise layer-to-layer alignment for advanced semiconductor structures.

-

Step 19 – Defect inspection and inline metrology: Throughout the manufacturing process, wafers are inspected using optical, X-ray, and electron-beam tools to detect defects such as particles, scratches, pattern misalignments, and thickness variations. In parallel, inline metrology tools measure critical dimensions, film thicknesses, and overlay accuracy at the nanometre scale to ensure each layer remains within specification. Early detection of these anomalies is essential for maintaining yield and preventing defects from propagating through subsequent process steps.

-

Step 22 – Wafer sort and electrical probe: After fabrication is complete, each individual die is electrically tested on the wafer using a probe card. This step, known as wafer sort, maps and records which dies pass or fail based on performance metrics. Good dies are marked electronically (inkless map), ensuring that only functional chips proceed to packaging.

-

Step 23 – Dicing / singulation: The wafer is cut into individual chips using a high-precision diamond saw or stealth laser dicing tool. Dicing must be exact to avoid chipping or cracking, which could compromise otherwise functional dies. Clean singulation is vital for achieving high packaging yields and long-term reliability.

These steps collectively ensure the structural integrity, pattern accuracy, and surface cleanliness required to maintain high manufacturing yield and chip performance. The extensive use of CMP, photolithography, and dry/wet etch processes makes this one of the most material- and consumable-intensive categories in the entire semiconductor process. These operations rely on high-purity chemicals, etchants, photoresists, abrasives, and inspection optics. Any error or contamination introduced here can propagate across layers, underscoring this stage’s importance in enabling successful lithography, interconnect formation, and final chip quality.

Key terms:

-

CMP (chemical mechanical planarisation): A technique that polishes surfaces to extreme flatness using chemicals and abrasives.

-

Photolithography: A light-based process for creating nanoscale circuit patterns onto a wafer.

-

Dielectric: An insulating material placed between metal layers to prevent short circuits.

-

Etch: A chemical or plasma-based process that removes selected materials from the wafer.

-

Wafer sort: Electrical testing of each chip on the wafer before packaging.

-

Dicing: Physically separating the wafer into individual chips.

6) Advanced packaging & assembly

Associated steps: 24, 25, 26, 27, 28, 29, 31, 32

Once a wafer has been processed and the individual chips have been tested and cut, they must be packaged. Packaging aims to protect the delicate chip, establish electrical connections to the outside world, and manage heat during operation. What was once a purely protective layer has now become a critical performance enabler, especially with the rise of 3D stacking, chiplets, and heterogeneous integration. This stage increasingly defines the performance envelope of modern chips, especially in advanced 2.5D and 3D architectures, where technologies like interposers, HBM (High-Bandwidth Memory), and chiplet-based design demand new packaging strategies. Material choices here directly influence electrical reliability, thermal conductivity, and integration density, making packaging a key differentiator in next-generation semiconductor devices.

-

Step 24 – Die attach: The individual chip (or "die") is physically attached to a package substrate or leadframe. This is typically done with an epoxy adhesive, conductive paste, or solder. The attachment method must provide both mechanical stability and good thermal conduction to pull heat away from the chip during operation.

-

Step 25 – Flip-chip attach / wire bond / micro-mump: This step forms the electrical connections between the chip and the package. There are multiple methods:

-

-

Wire bonding uses thin gold or copper wires to connect the die to the package pads.

-

Flip-chip bonding flips the die face down and connects it using solder bumps.

-

Micro-bumping is used in advanced 2.5D or 3D packaging to stack dies vertically with tiny interconnects.

-

-

Step 26 – Underfill and cure: For flip-chip packages, an underfill material is injected between the die and the substrate. This epoxy-based material protects the solder bumps from cracking during temperature changes and improves mechanical durability. After dispensing, the underfill is cured (hardened) in an oven.

-

Step 27 – Encapsulation or lid attach: The chip is sealed for protection using either:

-

-

Encapsulation involves moulding a plastic compound around the die.

-

Lid attach, often using a metal heat spreader for high-performance devices like CPUs or GPUs. This helps dissipate heat during operation.

-

-

Step 28 – Package back-grind and singulation: If the entire packaging process is done at the wafer level (known as WLP), the package stack is thinned by grinding from the back. This reduces thickness for mobile and compact applications. After thinning, individual packages are singulated (cut apart) for final handling.

-

Step 29 – Package test and burn-in: Each packaged chip is tested again under realistic operating conditions. Some devices are run through burn-in, where they operate at elevated temperatures and voltages for hours to screen out early-life failures. This helps ensure long-term reliability in the field.

-

Step 31 – Marking, tape-and-reel, or tray load: Functional chips are laser-marked with part numbers and lot information. They are then placed in trays or on reels, ready for high-speed assembly at electronics manufacturing plants.

-

Step 32 – Final quality control and outbound shipping: The finished, packaged chips undergo a final visual inspection and quality audit. They are vacuum-sealed in moisture-resistant packaging, often with desiccant and humidity indicators, and shipped to customers or contract manufacturers for board-level integration.

This stage has evolved far beyond physical protection. Advanced packaging now plays a decisive role in system performance, especially in AI, mobile, and high-bandwidth computing applications. Materials such as silver-filled die attach, low-CTE underfills, solder balls, polymer encapsulants, and metal lids are carefully selected to optimise thermal management, signal integrity, and mechanical durability.

Key terms:

-

Die: A single chip cut from the wafer.

-

Leadframe: A metal structure that supports the die and connects it to pins or solder pads.

-

Underfill: An epoxy that protects solder bumps and distributes mechanical stress.

-

Encapsulation: Protective sealing around the chip using plastic or epoxy resin.

-

Burn-in: Stress testing a chip to identify early failures before shipping.

-

Flip-chip: A packaging method where the die is flipped upside down and bonded using solder bumps.

7) Optical links, photonics & phosphors

Associated steps: 19, 30

While still a smaller share of the total manufacturing process, optical and photonic technologies are becoming increasingly important in advanced semiconductor applications. Traditionally, chips have relied solely on electrical signals. Still, new classes of devices now use or interact with light, whether to transmit data faster (optical interconnects), sense the environment (e.g. image sensors, lidar), or inspect critical features during manufacturing (optical metrology).

This category supports production-side inspection and system-level testing of chips that integrate light-based components. As data rates increase and electrical interconnects reach physical limitations, on-chip photonics, laser-based testing, and optical links become essential in sectors such as data centres, automotive vision systems, AI accelerators, and AR/VR.

-

Step 19 – Defect inspection and inline metrology (optical tools): In this step, advanced inspection systems use laser-based, X-ray, or electron-beam tools to detect defects in nanoscale chip structures. Many of these tools employ rare earth phosphors, such as gadolinium oxysulfide (Gd₂O₂S) or cerium-doped compounds, which convert radiation into visible light for detection. These phosphor-enhanced systems help identify missing lines, particles, voids, and pattern distortions in transistor layers and interconnect stacks. Without this high-resolution optical inspection, yield losses could go undetected until late in production.

-

Step 30 – System level test (SLT): SLT is the final functional test evaluates packaged chips under real-world conditions. This test ensures the chip operates correctly under expected workloads for devices incorporating photonics, such as silicon photonics transceivers, laser drivers, or optical sensors. Parameters such as laser alignment, photodiode sensitivity, optical I/O performance, and signal integrity are validated during SLT. This step is crucial for mission-critical applications in automotive cameras, lidar modules, AR/VR displays, and data centre switches, where failures cannot be tolerated.

As data speeds rise and traditional copper interconnects approach their physical and electrical limits, optical communication and on-chip photonics are emerging as critical next-generation solutions. These technologies enable faster, more efficient data transmission using light rather than electrical signals, reducing delay, power consumption, and crosstalk in high-density systems.

They rely on a growing set of specialised optical materials, including:

-

Germanium photodiodes for high-speed light detection

-

Indium phosphide (InP) lasers for optical transmission

-

Erbium-doped waveguides for light amplification within integrated circuits

In addition, rare earth elements such as gadolinium (Gd), erbium (Er), ytterbium (Yb), and europium (Eu) play essential roles, both as phosphor dopants in metrology and as active optical materials in photonics-enabled chips. These materials are increasingly used in data centre interconnects, AI accelerators, image sensors, telecom modules, and immersive computing platforms at the edge.

Key terms:

-

Photonics: A technology that uses light (photons) instead of, or alongside, electrical signals for faster data transmission and sensing.

-

Optical Interconnect: A light-based connection between chips or systems that replaces or supplements traditional copper wires.

-

Phosphors: Materials that glow or convert radiation into visible light, used in imaging systems and inspection tools.

-

System-level test (SLT): A final, full-function test run on the chip after packaging, often using real firmware and workloads.

Key Manufacturing Steps, Minerals and their Roles

0) R&D / design (EDA & IP)

The semiconductor manufacturing process begins well before any wafer enters a fabrication facility. It starts at the R&D and design stage, where engineers define chip architecture using Electronic Design Automation (EDA) tools and integrate pre-built IP blocks—reusable circuit elements like memory controllers or CPU cores, typically licensed from vendors such as Arm, Synopsys, or Cadence. This work occurs in a virtual environment, akin to computer-aided design (CAD) for silicon, powered by high-performance computing (HPC) infrastructure running the intensive simulations required to validate functionality, optimise performance, and prepare final layouts for tape-out.

Although no wafers are physically processed at this stage, the infrastructure enabling design work is constructed from the very materials and technologies that will be deployed downstream. The servers, GPUs, and storage systems at the heart of the design environment contain silicon, copper, gold, and rare earth magnets, reflecting the broader material dependencies of the semiconductor ecosystem. Evaluation platforms and prototyping kits used during this phase further expand the mineral footprint, incorporating compound semiconductors such as gallium arsenide (GaAs), indium phosphide (InP), and germanium, as well as infrared-sensitive materials like cadmium telluride (CdTe) and cadmium zinc telluride (CdZnTe).

This stage offers a significant performance advantage through computational iteration speed. Scalable simulation environments allow engineers to test more design variants, optimise energy efficiency, and push clock speeds, all before committing to fabrication. Decisions made here, around architecture, process node, packaging, and IP integration, lock in downstream material and process dependencies. They determine whether a chip will be built on a silicon or compound substrate, and which critical materials, gallium, hafnium, cobalt, tantalum, and others, will become essential.

The design workflow relies on three interdependent tool categories:

-

Compute clusters form the hardware backbone of the design environment. These HPC platforms consist of multicore CPUs, high-end GPUs, and high-bandwidth memory arrays arranged in parallel server farms, delivering petaflops of processing power. This compute capacity is essential for simulating modern system-on-chip (SoC) designs, which may contain billions of transistors and require detailed modelling of thermal, electrical, and timing behaviours across both micro and macro scales.

Key materials:

– Silicon (Si): Forms the chips inside CPUs and GPUs.

– Copper (Cu), Gold (Au): Enable signal routing and power delivery across server motherboards.

– Rare Earths (Nd, Dy, Tb): Used in high-strength magnets found in fans and HDDs.

– Iron (Fe), Boron (B): Structural alloys and magnetic compounds in server infrastructure

-

IP libraries are pre-verified, reusable logic blocks that reduce development time and risk while ensuring compatibility with specific foundry nodes through Process Design Kits (PDKs). Though intangible, their use has tangible consequences: selecting a GaN power IP core points to future use of gallium, nitride, and silicon carbide (SiC); deploying silicon photonics IP implies the eventual need for germanium, erbium, or indium phosphide during fabrication.

Material implications:

– Selecting a GaN power IP core implies downstream use of gallium, nitride, and silicon carbide.

– Deploying silicon photonics IP signals likely incorporation of germanium, erbium, or indium phosphide.

-

EDA software suites are the tools used to create, simulate, verify, and finalise chip designs. Vendors like Synopsys, Cadence, Siemens EDA, and Ansys offer integrated platforms that cover:

– Logic design (HDL editing, RTL synthesis)

– Simulation (timing, thermal, EM, signal integrity)

– Verification (formal, functional, coverage)

– Physical design (place-and-route, design rule checking)

– Mask generation (GDSII export, optical proximity correction)

While software-driven, these tools dictate how physical materials such as hafnium, cobalt, tantalum, and low-κ dielectrics, are spatially arranged within the final chip. Design constraints encoded in EDA platforms govern minimum spacing, metal widths, and compatibility with process nodes, directly shaping future material usage.

The types of semiconductors defined during this stage, whether logic (CPUs, GPUs, AI accelerators), memory (DRAM, NAND), analogue/mixed-signal, or optoelectronic/sensor/discrete devices (OSD), further shape material requirements. For example, high-speed RF amplifiers and laser diodes are typically designed on compound semiconductor platforms such as GaAs or InP due to their superior optoelectronic properties, necessitating the use of gallium, indium, and arsenic. By contrast, most logic and memory chips remain silicon-based, though even these increasingly depend on advanced materials at smaller nodes to sustain performance scaling.

Ultimately, the design phase functions as a strategic control point in the semiconductor value chain. It does not directly consume raw minerals in fabrication volumes, but it defines which materials will be required, in what form, and at what scale. From process node selection and IP licensing to substrate choice and device architecture, every decision made at this stage influences downstream demand for critical elements such as gallium, hafnium, cobalt, tantalum, and others.

Despite being simulation-heavy and digital in nature, the design environment already relies on a wide array of physical materials. High-performance compute clusters are built on silicon processors and copper interconnects, with gold contacts and rare earth magnets supporting data storage and thermal systems. Evaluation boards and test vehicles introduce compound semiconductors such as gallium, arsenic, indium, and germanium, while imaging and sensor prototypes incorporate cadmium, tellurium, and gadolinium. These materials prefigure the mineral and materials footprint that the manufacturing process must ultimately fulfil.

Material usage in R&D environments

Though this stage is digital and simulation-heavy, the underlying hardware and prototyping platforms rely on a wide range of critical and strategic elements, many of which foreshadow the materials required in manufacturing:

-

Silicon – Silicon is the foundational material of modern electronics, underpinning everything from simulation servers to prototyping boards. It forms the basis of CPUs, GPUs, and DRAM used in the high-performance compute clusters that power EDA workflows. Its ubiquity in the design environment reflects its unmatched role across logic, memory, and analogue domains.

-

Copper – Copper provides the dense, low-resistance interconnects inside server motherboards, GPUs, and networking switches used in design environments. It carries power and signals within and between components and is vital to the thermal performance of large compute systems. Copper also appears in PCB traces, evaluation boards, and IP test platforms used during early design validation.

-

Gold - Gold is used in bonding wires, connector plating, and socket interfaces within HPC systems and prototyping environments. Its exceptional corrosion resistance and conductivity make it the metal of choice for reliable, long-life electrical contacts, ensuring stable performance in data centres, test jigs, and evaluation boards used in early-stage chip bring-up.

-

Neodymium – Neodymium, often alloyed with dysprosium and boron (as NdFeB), forms the permanent magnets in hard disk drives and high-torque cooling fans found in EDA compute clusters. These magnets enable compact, high-power motors that deliver the mechanical performance required for server-grade thermal and data storage systems.

-

Iron – Iron is a primary component in server chassis, magnetic cores in power inductors, and structural frameworks used in R&D infrastructure. In magnet alloys (e.g., NdFeB), iron contributes to the high saturation magnetisation essential for dense, efficient cooling fans and storage drives, critical for the uptime and thermal management of EDA clusters.

-

Boron – Boron plays a dual role in R&D environments: as a dopant in reference wafers or test chips used for process calibration, and as part of the NdFeB magnets in fan motors and HDDs. Boron enhances coercivity in magnets and is fundamental to p-type doping strategies that designers may explore virtually using TCAD and other device simulation tools.

-

Gadolinium – Gadolinium may appear in x-ray or thermal imaging prototypes evaluated during early device R&D. Its high neutron capture cross-section and unique magnetic properties make it a component of Gd₂O₃ or GdOS scintillators used in image sensors and inspection tools. Gd-based materials also appear in high-resolution diagnostic systems that support chip debugging.

-

Arsenic – Arsenic is a key dopant in III–V compound semiconductors like GaAs and InGaAs, which are frequently used on prototyping boards for RF, optical, and high-speed data applications. In R&D, test vehicles based on GaAs or InP substrates embed arsenic-rich compounds to enable fast switching and light emission—vital for validating IP used in photonics and RF front ends.

-

Indium – Indium is central to indium phosphide (InP) and indium tin oxide (ITO) technologies used in optical transceivers, laser drivers, and test vehicles for data communications. Design-stage platforms exploring photonic integration often include In-based materials, and indium-soldered optical components are commonly mounted on evaluation boards.

-

Germanium – Germanium plays an important role in SiGe test chips and prototype modules, especially where stress engineering or optical sensitivity is required. Early-stage performance validation for mixed-signal or photonic IP may use Ge-containing devices to explore high-speed behaviour, making Ge an indirect but strategic material in design-driven evaluation.

-

Tellurium – Tellurium appears in cadmium telluride (CdTe) and phase-change memory (GeSbTe) materials that are sometimes explored in emerging memory or IR sensor designs. Evaluation platforms for thermal imagers, edge AI sensors, or neuromorphic computing may use Te-containing chips, particularly in R&D centres focused on defence, medical, or aerospace applications.

-

Cadmium – Cadmium is used in CdTe and CdZnTe substrates for infrared detectors and X-ray imagers, technologies frequently evaluated in sensor-focused R&D labs. Cd-containing materials offer high quantum efficiency in long-wave infrared, making them key to early-stage prototyping for space, automotive, and surveillance applications.

The R&D and design phase is a critical upstream checkpoint where material footprints are implicitly defined. Through tool selection, IP licensing, and simulation choices, this stage determines what the fab will need and how the downstream supply chain must respond. It is the point where innovation and critical mineral demand first intersect.

EDA software suites: Core functions and material implications

EDA software suites are the central tools used to design, simulate, verify, and finalise semiconductor devices before fabrication. Developed by leading vendors such as Synopsys, Cadence, Siemens EDA, and Ansys, these platforms support the entire design flow, from high-level logic definition to physical layout and photomask preparation. Each stage within the suite has distinct responsibilities, and together they ensure the final chip design is functionally correct, manufacturable, and material-aware.

The five key domains of EDA functionality are outlined below, with further detail on how each contributes to the design process and influences downstream material demand:

1. Logic design (HDL editing, RTL synthesis)

Logic design is the first step in the digital design process, where engineers define the chip’s functional behaviour using hardware description languages (HDLs) such as Verilog or VHDL.

This begins with HDL editing, in which designers write code that describes how components like ALUs, memory controllers, or processor cores should behave, capturing logic operations, state transitions, and data flow. Once the high-level logic is defined, RTL (Register Transfer Level) synthesis converts it into a gate-level netlist, a map of logical elements such as flip-flops, multiplexers, and combinational gates. This netlist is then optimised for area, speed, and power.

Decisions made during logic design affect gate count, clock frequency, and power efficiency, all of which directly impact the physical die area, thermal load, and ultimately material demand in manufacturing, for instance, influencing the quantity of copper needed for interconnects or the use of hafnium-based high-κ dielectrics in transistor gate stacks.

2. Simulation (timing, thermal, EM, signal integrity)

Simulation assesses how a chip design will perform under real-world electrical, thermal, and physical conditions, long before it reaches silicon. This phase ensures that the design is not only functionally correct, but also electrically stable, thermally manageable, and signal-accurate at scale.

-

Timing simulation checks that signals propagate through logic paths within the bounds of a clock cycle, flagging any setup or hold violations that could cause functional errors.

-

Thermal simulation models how heat is generated and dissipated across the die, influencing layout decisions and the need for materials such as copper redistribution layers or indium-based thermal interface materials (TIMs) in packaging.

-

Electromagnetic (EM) simulation evaluates inductive and capacitive coupling between metal lines and components, identifying risks related to signal degradation, power integrity, or electromagnetic interference (EMI).

-

Signal integrity simulation ensures clean transitions along interconnects, detecting issues like glitches, overshoot, ringing, or crosstalk that can impair high-speed operation.

These simulation results directly inform the design of the power distribution network (PDN), routing strategies, and shielding requirements, factors that ultimately dictate the materials, thicknesses, and stack-ups used in the back-end-of-line (BEOL). From copper interconnects and low-κ dielectrics to barrier metals, simulation choices shape the physical material footprint of the chip.

3. Verification (formal, functional, coverage)

Verification is a strategic filter for resource efficiency, materially reducing the consumption of critical minerals and chemicals across the manufacturing process. It ensures that a chip behaves exactly as intended under all operating conditions, catching logic or design errors before fabrication begins. This stage provides functional correctness, logical completeness, and confidence that the design will operate reliably in real-world systems.

-

Formal verification uses mathematical techniques to prove that specific properties always hold—such as ensuring that a signal will never short, a register will always reset, or that illegal states are unreachable.

-

Functional verification relies on simulation and testbenches to validate that the design behaves as expected in practice, for example, confirming that a CPU core correctly executes instructions or that a peripheral interface responds to input in real time.

-

Coverage verification evaluates how comprehensively the logic has been exercised, measuring metrics like the percentage of branches, states, conditions, and paths that have been tested.

Together, these three verification methods form a critical safeguard against design flaws. Errors identified at this stage prevent costly mask re-spins, eliminate the risk of fabricating defective silicon, and avoid downstream waste of high-value materials such as photoresists, reticles, and ultra-pure wafers.

4. Physical design (place-and-route, design rule checking)

Physical design is the stage where a chip's logical structure is translated into a precise physical layout on a silicon wafer. It bridges abstract circuit behaviour with manufacturable geometries, defining the chip's physical footprint, interconnect architecture, and metal layer usage. It is a primary determinant of manufacturing cost and material efficiency.

-

Place-and-route (P&R) determines the location of logic blocks and routes the interconnects that link them. It specifies exact wire lengths, via placements, metal stack utilisation, and spatial relationships—factors that directly influence delay, power, and die area.

-

Design Rule Checking (DRC) ensures all layout geometries conform to foundry-defined manufacturing constraints, including minimum spacing, line width, overlay tolerances, and alignment rules for lithography and etch steps.

This phase is foundational to material consumption. It dictates the quantity and distribution of metals and dielectrics, such as copper, tungsten, cobalt, tantalum, hafnium, and low-κ materials, across the back-end-of-line (BEOL) stack. Strict DRC compliance is essential to avoid yield-limiting defects and lithographic failures, reduce rework, conserve high-value substrates, and minimise waste of critical materials during wafer processing.

5. Mask generation (GDSII export, optical proximity correction)

Mask generation is the final stage of the physical design process, where layout data is prepared for high-precision photolithography. It transforms a digital blueprint into a manufacturable form by producing the files and optical corrections required to guide mask fabrication and scanner operation.

-

GDSII export converts the verified physical layout into a standardised format used to fabricate photomasks. These masks define where specific materials—such as metals, dielectrics, and dopants—will be patterned, etched, or deposited on the wafer.

-

Optical Proximity Correction (OPC) adjusts geometric shapes in the layout to counteract distortions caused by diffraction and process limitations during lithography. Without OPC, features printed on silicon would deviate from their intended dimensions, particularly at advanced nodes.

OPC is indispensable at feature sizes below 10 nanometres, where EUV or ArFi lithography is required. More aggressive OPC results in greater pattern complexity, which in turn drives up the demand for advanced materials: molybdenum, chromium, and quartz for photomasks, and tin, ruthenium, and fluorine for scanner operation. Mask generation is thus a critical inflection point where data, optics, and material science converge, shaping both the precision of pattern transfer and the intensity of upstream mineral usage.

Stage 1) Silicon Crystal Growth (Monocrystalline Silicon Ingot)

Functional category: Wafer Formation & Doping (front-end substrate)

Step 1) Silicon crystal growth (monocrystalline silicon ingot)

Wafer fabrication is the heart of semiconductor manufacturing, where designed circuits are physically realised on silicon wafers inside a fabrication facility. This stage is capital- and materials-intensive, involving hundreds of discrete process steps and highly specialised equipment. A single chip may require over 500 manufacturing stages and depend on supply chains that cross dozens of international borders. Fabrication begins with the formation of the wafer itself, a precision-engineered substrate that underpins every layer of the integrated circuit.

Silicon wafers constitute the dominant substrate in modern semiconductors. Silicon is abundant in the Earth's crust, typically found as silica (SiO₂), but must be refined into ultra-high purity polysilicon before being grown into large single-crystal ingots. These ingots are the base material for all mainstream CMOS logic and memory chips. While alternative materials such as gallium arsenide or silicon carbide are used in specialised applications, silicon remains unmatched in performance-to-cost ratio, offering excellent carrier mobility, a high-quality native oxide, and mature process control.

The crystal growth process typically begins with 11N-grade polysilicon, which is melted in a high-purity quartz crucible. A seed crystal is then inserted and slowly pulled from the melt at approximately 1 mm per minute, forming a defect-free monocrystalline ingot, or boule, weighing between 150 and 450 kilograms. This is known as the Czochralski process, which dominates logic and memory wafer production. Float-zone growth is an alternative method used in niche high-voltage or high-resistivity applications where ultra-low contamination is required.

The Czochralski growth chamber is surrounded by an inert argon atmosphere, which prevents oxidation and contamination of the silicon melt. During the pull, minute quantities of dopants, typically boron, phosphorus, or arsenic, are introduced to control the wafer’s electrical properties. Boron (Group III) creates p-type material by generating holes, while phosphorus and arsenic (Group V) contribute electrons to form n-type material. These dopants establish the wafer’s baseline resistivity and carrier type, reducing the number and complexity of implantation steps required later in fabrication.

The quartz crucible contains the silicon melt and introduces trace oxygen levels into the crystal. While generally considered an impurity, oxygen at controlled levels strengthens the crystal lattice and creates internal gettering sites that trap metallic contaminants. The furnace assembly often incorporates graphite components to support the crucible and deliver heat. Some carbon from these elements may diffuse into the silicon at parts-per-billion levels, which can influence crystal defectivity but is often tolerated within control limits.

In some cases, nitrogen gas is introduced into the ambient environment to improve crystal quality. Nitrogen-doped silicon wafers exhibit reduced void defects, improved mechanical strength, and enhanced internal gettering performance. These attributes are particularly valuable in advanced CMOS nodes, where even sub-micron lattice irregularities can impact device yield.

The resulting single-crystal silicon ingot is cooled, extracted, and further processed. It is sliced into wafers, shaped, polished, and cleaned to meet the exacting standards required for front-end fabrication. The entire process is highly sensitive to impurity levels, thermal gradients, and mechanical stress. Any defect introduced at this stage carries forward through all subsequent manufacturing steps, making crystal growth one of the most critical control points in the semiconductor supply chain.

-

Silicon – Silicon is the foundational material for nearly all semiconductor devices. It is refined from quartz sand, or silicon dioxide, into high-purity polysilicon, which is then melted and grown into single crystals, typically by the Czochralski process. Silicon remains dominant due to its low cost, excellent native oxide (SiO₂), high charge carrier mobility, and a mature ecosystem of process control and tooling. These properties make it uniquely suited to high-volume CMOS manufacturing, outperforming III–V wafers in scalability and reliability for most logic and memory applications. In addition to these performance benefits, silicon is compatible with advanced lithography and doping techniques, making it essential for transistor scaling and dense integration. No other material combines electrical performance, mechanical robustness, thermal conductivity, and process maturity in the same way.

-

Oxygen - Oxygen is unintentionally but beneficially introduced into the silicon lattice during crystal growth, primarily from the quartz crucible. In trace amounts, oxygen atoms occupy lattice vacancies, which helps to stabilise the crystal structure and strengthen the wafer mechanically. More importantly, oxygen can create internal gettering sites, which are regions that trap metallic impurities and prevent them from affecting active device areas during later processing steps. This gettering capability is vital to device reliability, especially in high-performance and low-defect-yield nodes. Oxygen, although technically an impurity, functions as a structural enhancer and a defect management tool during both crystal formation and downstream fabrication.

-

Quartz (SiO₂) – Quartz is used to make the crucible that holds the molten silicon during the Czochralski pull. It is chosen for its chemical purity, thermal stability, and ability to withstand prolonged exposure to molten silicon at approximately 1,400 degrees Celsius. However, quartz also contributes trace amounts of oxygen impurities, on the order of 10¹⁸ atoms per cubic centimetre, to the growing crystal. This controlled oxygen incorporation is critical for wafer strength, dislocation suppression, and impurity gettering. As a result, quartz serves both a structural and chemical role, enabling the production of high-quality silicon ingots through its direct interaction with the melt and its containment function.

-

Dopant elements (B, P, As) – Controlled amounts of boron, phosphorus, and arsenic are introduced to define the electrical properties of the wafer from the outset. Boron, a Group III element, creates p-type silicon by introducing holes as majority carriers. Phosphorus and arsenic, both Group V elements, create n-type material by donating electrons. Doping the melt during crystal growth allows for precise control of resistivity and carrier concentration, reducing the number and complexity of later ion implantation steps. This approach also improves uniformity across the ingot, leading to better electrical consistency across dies and higher overall wafer yield. The dopant mix can be tailored to meet specific requirements, whether for low-leakage logic, fast-switching memory, or high-voltage power applications.

-

Inert gases (Ar) – Argon provides an inert atmosphere within the crystal growth chamber. By displacing oxygen and moisture in the ambient, argon prevents oxidation of the silicon melt and minimises contamination from air or furnace components. It also helps to maintain a stable thermal environment, which is essential for consistent ingot growth and uniform crystal quality. As a noble gas, argon is chemically inert, and its use ensures that reactive species are excluded from the environment, preserving the purity of both the melt and the growing crystal.

-

Graphite (C) – Graphite is used for furnace components such as heater coils, crucible supports, and insulation, due to its high-temperature stability and low chemical reactivity. While graphite is not intended to contribute to the melt composition, trace amounts of carbon can dissolve into the silicon at concentrations around 10¹⁷ atoms per cubic centimetre. If properly managed, this small amount of carbon can have neutral or even beneficial effects, such as contributing to lattice hardening or interacting with oxygen to stabilise dislocation structures. However, excess carbon can increase the risk of defect formation, so its presence must be tightly controlled through furnace design and ambient management.

Nitrogen (N) – Nitrogen is sometimes introduced into the ambient environment during crystal growth to improve crystal quality. Nitrogen atoms occupy interstitial sites in the silicon lattice, which can suppress the formation of voids, pin dislocations, and enhance the formation of internal gettering sites. Nitrogen-doped silicon wafers exhibit improved mechanical strength, better thermal stability, and reduced defect density, all of which contribute to higher yields in downstream fabrication. These properties are particularly valuable in advanced CMOS nodes and high-voltage applications, where even minor lattice irregularities can significantly affect device performance and long-term reliability.

Step 2) Ingot trim & grind (conditioning the crystal)

Once the monocrystalline silicon ingot has been grown and cooled, it undergoes a series of mechanical conditioning steps to prepare it for wafer slicing. The ingot is first trimmed to remove the seed and tail sections, which typically contain defects or irregularities introduced at the start and end of the pull. It is then centre-ground to achieve a uniform diameter, ensuring compatibility with automated wafer handling systems.

To establish orientation, one or more flats or notches are laser-scribed along the length of the ingot. These serve as reference points for every downstream tool, enabling correct wafer alignment during photolithography, doping, and etching steps. After grinding, the ingot may also undergo chemical edge etching and surface inspection to remove slip lines, dislocations, or surface defects, and to verify oxygen striation patterns. These inspections ensure the crystal meets strict structural and dimensional specifications before slicing begins.

The grinding process uses ultra-hard abrasive materials, primarily synthetic diamond and silicon carbide (SiC). Synthetic diamond, produced through high-pressure high-temperature (HPHT) or chemical vapor deposition (CVD) methods, is used for both trimming and centreless grinding wheels. Its extreme hardness enables sub-micron surface flatness and reduces the risk of micro-cracking at the wafer edge. Silicon carbide abrasives may also be used for intermediate grinding steps or edge bevel processing, offering a reliable and cost-effective complement to diamond-based tools.

Proper conditioning at this stage is critical to minimising mechanical stress and avoiding wafer breakage in later steps. A well-prepared ingot dramatically reduces handling-related yield loss and maintains geometric precision across the wafer batch, making this one of the key mechanical checkpoints in the wafer supply chain. When correctly executed, ingot trimming and grinding reduce total wafer breakage to only a few parts per million.

Diamond and silicon carbide (SiC) abrasives are essential materials used in the mechanical conditioning of silicon ingots due to their exceptional hardness and wear resistance.

-

Diamond (C) – Synthetic diamond, the hardest known material, is used in grinding wheels, wire saws, and slicing blades to achieve sub-micron surface precision during centre grinding, edge shaping, and wafer slicing. Its ability to maintain a sharp cutting profile under high load ensures consistent material removal rates, minimal chipping, and excellent surface flatness, all of which are critical to reducing defect propagation in later processing.

-

Silicon carbide (SiC) – Silicon carbide is also widely used as an abrasive material in semiconductor processing. Though softer than diamond, SiC offers an ideal balance of cutting power, thermal stability, and cost-effectiveness. It is commonly used in intermediate grinding steps, edge beveling, and surface conditioning, where slightly less aggressive abrasion is sufficient. SiC abrasives help remove damage layers from earlier mechanical operations and prepare the ingot for chemical etching and inspection. Its relatively low cost compared to diamond makes it especially valuable in high throughput grinding environments where abrasive wear is a factor. SiC supports precise material removal while helping to control surface stress and defect formation.

Stage 2) Wafer Slicing and Preparation (Ingot to Polished Wafer)

Functional category: Wafer Formation & Doping (front-end substrate)

Step 3) Wafer slicing & edge shaping

Once the monocrystalline silicon ingot has been trimmed and ground, it is sliced into thin wafers using high-precision cutting tools. The most common method is a multi-wire saw, where a continuous loop of fine wire coated with synthetic diamond abrasives moves through a slurry or abrasive fluid to slice the ingot into wafers approximately 675 micrometres thick. These wire saws offer minimal kerf loss, tight thickness control, and excellent surface quality. For smaller-diameter ingots, such as 150 mm, inner-diameter (ID) saws may still be used.

After slicing, wafers undergo edge shaping to chamfer and round the perimeter to a typical radius of 300 micrometres. This step reduces the formation of micro-cracks, suppresses bevel contamination, and improves mechanical strength during handling. Carefully controlling the bevel profile minimises stress concentrations that could otherwise lead to wafer breakage in later thermal or mechanical processing steps.

This stage relies on ultra-hard tools, particularly diamond-coated wires and precision edge grinders, to achieve sub-micron tolerances and clean surface finishes. The goal is to produce geometrically uniform wafers, mechanically robust, and ready for flattening and polishing in the next stage.

-

Diamond(C) – Diamond is the hardest known material and offers exceptional wear resistance, making it uniquely suited for slicing brittle materials such as silicon. In wafer manufacturing, synthetic diamond abrasives are bonded to wire saws and grinding tools to enable clean, efficient, and repeatable cutting. Diamond's hardness allows it to cut through silicon's crystal lattice without excessive tool wear or mechanical damage, enabling high dimensional accuracy and tight thickness control. Diamond-coated wires also minimise kerf loss, the material wasted during slicing, which helps maximise wafer yield from each ingot.

Additionally, diamond abrasives reduce mechanical vibration during cutting, which lowers the risk of introducing micro-cracks or subsurface damage that could affect wafer performance downstream. In the edge-shaping process, diamond grinding tools provide the precision needed to chamfer and round the wafer edge, a critical step for reducing stress concentrations, particle generation, and handling-related breakage. The extreme durability of synthetic diamond ensures consistent performance and long tool life, improving overall process stability and equipment uptime.

Step 4) Wafer flattening

After slicing, the silicon wafers must be flattened and polished to achieve the extreme surface planarity required for nanometre-scale lithography. This stage removes saw marks, topographic variation, and sub-surface damage, and ensures that each wafer is dimensionally uniform across its entire surface.

The process begins with double-side grinding, typically reducing 300 mm wafers to a target thickness of approximately 725 micrometres. This is followed by lapping, a mechanical abrasion process that improves parallelism between the wafer faces. Once the wafer is mechanically conditioned, it undergoes chemical mechanical planarisation (CMP) using slurries that contain colloidal silica (SiO₂), alumina (Al₂O₃), or ceria (CeO₂). CMP polishes the wafer to achieve a total thickness variation (TTV) of less than 0.2 micrometres and a surface roughness (Ra) below 0.12 nanometres. This level of flatness is necessary to maintain lithographic focus and overlay alignment across the entire die field.

Following CMP, wafers are cleaned using a sequence of wet chemical processes, including megasonic cleaning and RCA cleaning protocols such as SC-1 (NH₄OH + H₂O₂ + H₂O) and SC-2 (HCl + H₂O₂ + H₂O). These cleans remove particulate contamination, organic residues, and metallic ions, often reducing trace metal concentrations to below 0.06 parts per trillion (ppt). A final HCl rinse is often used to strip residual metal contaminants from the wafer surface.

This step is highly dependent on specialised consumables and toolsets, including CMP polishers, slurry delivery systems, and megasonic tanks. Abrasives such as ceria (CeO₂), a rare earth oxide, are preferred for their high oxide removal rates, while zirconia (ZrO₂) nanoparticles are used in later stages for high-k metal gate polishing. Other critical chemicals include hydrofluoric acid (HF), potassium hydroxide (KOH), and chlorine-based etchants.

-

Silicon Dioxide (SiO₂) – Silicon Dioxide (SiO₂) is a widely used abrasive in chemical mechanical planarisation (CMP) slurries. Its fine particle size and relatively low hardness allow for gentle, uniform polishing of silicon wafer surfaces, particularly during oxide removal steps. SiO₂ provides a balanced removal rate and low defectivity, making it ideal for applications where surface planarity and minimal damage are critical.

-

Aluminium Oxide (Al₂O₃) – Aluminium Oxide (Al₂O₃) serves as both a CMP abrasive and a lapping medium. Harder than silicon dioxide, Al₂O₃ is used when more aggressive material removal is needed, such as during initial flattening or in cases where tougher layers must be planarised. Its high mechanical durability also makes it effective in earlier grinding stages and when processing harder dielectric stacks.

-

Ceria (CeO₂) – Ceria (CeO₂) is a high-performance abrasive that offers the fastest oxide removal rates among CMP materials. It is especially effective at polishing thermal silicon dioxide and is crucial for achieving Ångström-level surface flatness. As one of the few rare earth compounds used in front-end semiconductor processing, ceria is valued for its high oxide-to-silicon selectivity, low defectivity, and its ability to maintain tight process control at advanced nodes.

-

Zirconium Oxide (ZrO₂) – Zirconium Oxide (ZrO₂) is a nanoparticle abrasive used in the planarisation of high-k dielectrics and metal gate stacks, particularly in advanced logic nodes. Though not a rare earth element, ZrO₂ behaves similarly in nanoscale form, offering excellent control and low scratch rates during high-precision CMP steps. It is commonly used in polishing processes for high-k metal gate (HKMG) structures, where defect-free surfaces are essential.

-

Hydrofluoric Acid (HF) – Hydrofluoric Acid (HF) is a powerful wet etchant used to remove native oxide films from silicon surfaces. Following CMP, residual silicon dioxide layers must be eliminated to prepare the wafer for further processing steps such as epitaxial growth or dielectric deposition. HF’s selectivity and reactivity make it indispensable for final cleaning and surface conditioning.

-

Potassium Hydroxide (KOH) – Potassium Hydroxide (KOH) functions as both an etchant and a cleaning agent in wafer processing. It anisotropically etches silicon, creating well-defined surface features for MEMS or trench structures, and is also used in combination with oxidisers and surfactants for precision cleaning. Its compatibility with silicon surfaces makes it a useful component in both batch and wet bench cleaning processes.

-

Chlorine (Cl) (in HCl rinse) – Chlorine (Cl), often delivered via hydrochloric acid (HCl), is used to remove residual metallic contaminants from wafer surfaces. Chlorine forms volatile metal chlorides with trace elements like iron and copper, allowing them to be rinsed away. This step is critical for achieving ultra-low metal ion levels before device fabrication begins, preventing electrical leakage and reliability issues.

-

Water (H₂O) – Water (H₂O) is the universal solvent in semiconductor cleaning and slurry systems. It serves as the carrier for etchants, cleaning agents, and abrasives, and plays a vital role in controlling chemical concentrations, cooling reaction zones, and flushing away residues. Ultrapure water (UPW) is used throughout the process to maintain strict contamination control.

Stage 3) Front-End-of-Line (FEOL) – Transistor Fabrication

Functional categories: Wafer Formation & Doping, Active Device Layers, Gate Stack (High-k & Ferroelectric)

Step 5) Epitaxial layer growth

In this step, a thin, defect-free crystalline layer is grown on top of the silicon wafer surface. This epitaxial layer, or "epi", serves as the foundation for high-performance transistor channels in advanced CMOS nodes, and is also critical for power, analogue, and radio frequency (RF) devices requiring low-defect active layers.

The process typically uses reduced-pressure chemical vapour deposition (RPCVD) or low-pressure CVD (LPCVD) systems operating between 650°C and 1,050°C. During deposition, gases such as dichlorosilane (SiH₂Cl₂), hydrochloric acid (HCl), germane (GeH₄), and sometimes deuterium (D₂) are introduced to form layers of silicon (Si), silicon-germanium (Si₁₋ₓGeₓ), or other compound semiconductors. The result is a highly controlled film with precisely engineered composition and lattice strain, often 10–30 nanometres thick for Si caps or 20–40 nanometres for SiGe.

Strain engineering is a central goal of epitaxy at advanced nodes. By adjusting the germanium or carbon content, engineers can induce tensile or compressive strain in the channel region, improving carrier mobility and overall transistor performance. For example, SiGe layers introduce compressive strain for PMOS, while Si:C (carbon-doped silicon) creates tensile stress for NMOS. Materials like GeSn are being explored for high-mobility p-type field-effect transistors (PFETs) in more advanced applications.

In specialty applications, epitaxy grows II–VI semiconductor compounds such as cadmium telluride (CdTe) or cadmium zinc telluride (CdZnTe). These materials are essential for infrared detectors, X-ray sensors, and other optoelectronic systems. Additionally, deuterium (D₂) is now used in some gate-last process flows to passivate hot-carrier traps, significantly improving long-term reliability.

-

Silicon – Silicon is the foundational element for epitaxial growth in most semiconductor devices. In Step 5, epitaxial silicon layers are grown atop the wafer to create ultra-pure, low-defect starting surfaces for transistor formation. This enables precise doping control, reduces crystal dislocations, and improves junction isolation. In advanced logic nodes, ultra-thin Si layers are also used as caps above strain-engineered layers to protect the channel and enhance mobility.

-

Germanium – Germanium is incorporated into epitaxial layers to form silicon-germanium (SiGe) alloys, which induce compressive strain in p-type (PMOS) transistor channels. This strain improves hole mobility, resulting in faster switching and lower drive voltage. In addition, germanium is used in high-mobility GeSn alloys for emerging PFET channels, particularly in sub-5 nm nodes and advanced FinFET or nanosheet architectures.

-

Hydrogen - Hydrogen is a standard component in CVD gas flows, acting as a carrier gas, surface passivator, and etch modulator. During epitaxy, hydrogen helps prevent unwanted oxide formation, promotes smooth crystal growth, and assists in removing volatile by-products like SiCl₄. It also terminates dangling bonds at the surface, improving epitaxial layer quality.

-

Chlorine – Chlorine is introduced as hydrochloric acid (HCl), which serves multiple purposes in epitaxy. It etches excess silicon, helps maintain a smooth surface, and removes contaminants during the growth cycle. Chlorine reacts with unwanted impurities to form volatile chlorides that can be purged from the chamber, resulting in ultra-clean, defect-free layers.

-

Carbon – Carbon is added to epitaxial silicon to form Si:C stressors, introducing tensile strain into n-type (NMOS) transistor channels. This tensile strain enhances electron mobility, improving switching speed and reducing resistance. Carbon’s small atomic radius allows it to substitute into the silicon lattice without excessive defect generation, making it a precise strain-engineering tool for high-performance logic devices.

-

Tin – Tin is used in germanium–tin (GeSn) alloys for next-generation p-type channels. Adding tin to germanium reduces the bandgap and enhances hole mobility, making GeSn attractive for high-performance PFETs. Sn incorporation enables lower power operation and compatibility with future nanosheet or vertical device architectures.

-

Cadmium – Cadmium is used in compound semiconductor materials like cadmium telluride (CdTe) and cadmium zinc telluride (CdZnTe) grown epitaxially for infrared sensors and X-ray detectors. Cd enables high absorption efficiency and sharp energy resolution, making it essential for imaging and optoelectronic applications that demand precise material control.

-

Tellurium – Tellurium is combined with cadmium to form CdTe or CdZnTe epitaxial films. These II–VI semiconductors have excellent optical properties and are ideal for infrared, X-ray, and thermal imaging sensors. Te contributes to high carrier mobility and spectral sensitivity, especially in long-wavelength detection applications.

-

Zinc – Zinc is often alloyed with CdTe to form CdZnTe, a tunable material for high-resolution photodetectors. Zinc helps adjust the bandgap and mechanical properties of the crystal, improving detector efficiency and compatibility with integration schemes. Zn also enhances lattice matching and reduces dislocation density in the final epitaxial layer.

-

Deuterium – Deuterium, a heavy isotope of hydrogen, is increasingly used in advanced gate-last process flows following epitaxial growth. When incorporated into the silicon lattice or gate stack, deuterium is more stable than hydrogen and effectively passivates hot-carrier traps, significantly enhancing device reliability. It is vital in ultra-scaled transistors where stress-induced leakage and charge trapping can degrade performance over time.

Step 6) Front-side oxidation / pad oxide

In this step, a thin layer of silicon dioxide (SiO₂) is thermally grown on the silicon wafer surface to serve as a sacrificial or pad oxide. This layer acts as an initial insulating barrier, protects the wafer during early lithography steps, and supports isolation mask formation for defining active device regions. The pad oxide is critical for advanced logic and power nodes, providing a clean, controlled surface that enhances device performance by reducing defects and contamination.

The process typically employs oxidation furnaces operating at 800–1100°C, using dry oxygen (O₂) or wet steam (H₂O) to grow a 5–20 nm SiO₂ layer. Dry O₂ oxidation is preferred for its precise control over thickness and uniformity, producing a high-quality dielectric with minimal impurities. The reaction (Si + O₂ → SiO₂) consumes silicon from the wafer surface, simultaneously smoothing epitaxial defects and gettering residual metallic contaminants, which improves surface quality and device reliability. Wet oxidation with H₂O may be used for thicker layers when speed is prioritised over precision.

Oxygen (O₂) is the key reactant in this step, enabling the formation of a dense, uniform SiO₂ layer with excellent insulating properties. This layer isolates active regions, preventing unwanted electrical interactions, and serves as a cushion for subsequent processing steps, such as nitride deposition or ion implantation. The precise control of O₂-based oxidation ensures the thin pad oxide meets the stringent requirements of advanced nodes, where even minor variations can impact yield and performance.

In some process flows, the pad oxide also facilitates strain engineering by providing a stable base for subsequent layers, such as silicon nitride, used in shallow trench isolation (STI). The SiO₂ layer's ability to passivate the surface further enhances long-term device reliability by reducing leakage currents and improving junction isolation.

-

Oxygen – Oxygen is the foundational element for thermal oxidation in this step. O₂ reacts with the silicon wafer to form a high-quality SiO₂ pad oxide layer, insulating surface that protects the chip, reduces defects, and sets the stage for building advanced semiconductor devices.

Step 7) Shallow-trench isolation (STI)